#### Advanced NEMFET-based Power Management for deep-submicron Integrated Circuits

#### Sorin Cotofana and Marius Enachescu

Computer Engineering Laboratory Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology (TU Delft), The Netherlands

Computer Engineering Laboratory 先端ハイブリッドナノデバイス国際シンポジウム International Symposium on Advanced Hybrid Nano Devices (IS-AHND)

- CMOS technology is approaching its physical limits.

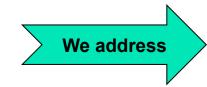

- Emerging technologies have been investigated and proposed to supersede the MOSFET, e.g., Nano-Electro - Mechanical FETs (NEMFETs), carbon nanotubes, quantum dot cellular automata, single-electron devices.

- Only low complexity circuits were successfully designed with the above technologies.

- 3D-Stacked IC (3D-SIC) may provide a smooth transition between CMOS and emerging devices.

- It is a technology that potentially provides heterogeneous integration, higher performance, and lower power consumption, when compared to planar ICs.

- Scaling CMOS technology could still provide 30% improvement in performance at the 28 nm node with respect to the 40 nm node.

- Tremendous increase of power dissipation of digital CMOS.

- The life of the battery operated embedded systems with low activity, which is mostly determined by the standby leakage power dissipated by the circuit in sleep mode, is directly affected.

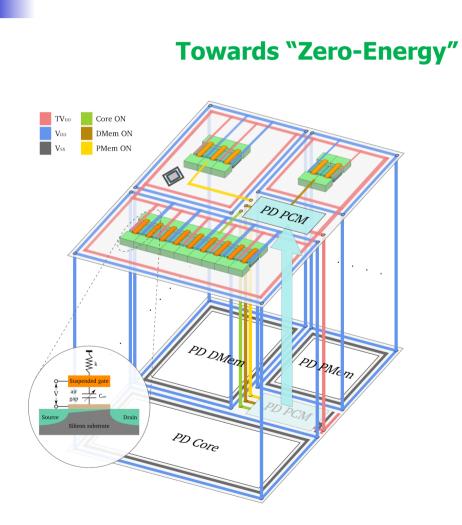

A Hybrid CMOS-NEMS 3D Stacked Chip Power Management Architecture.

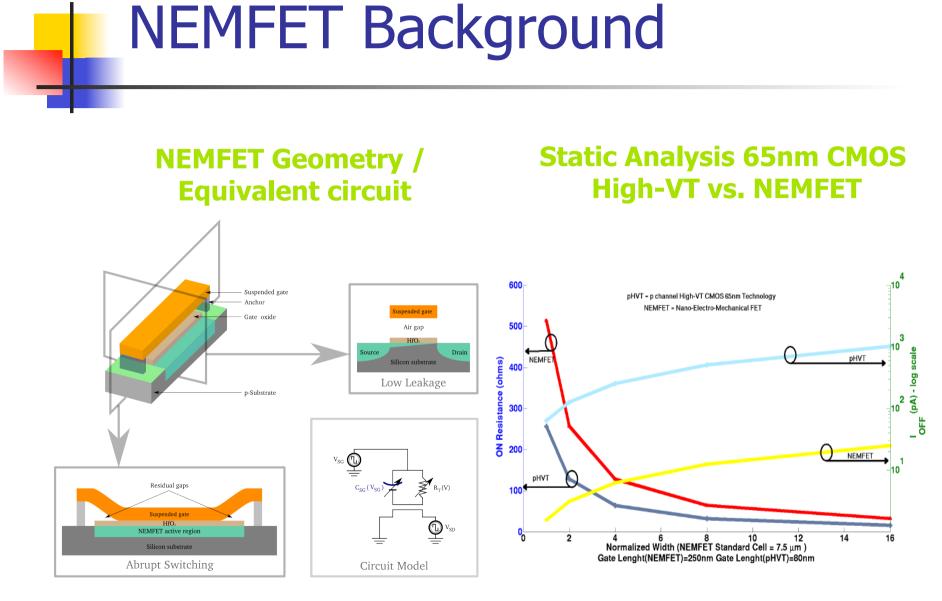

#### **NEMFET Dynamic Behavior**

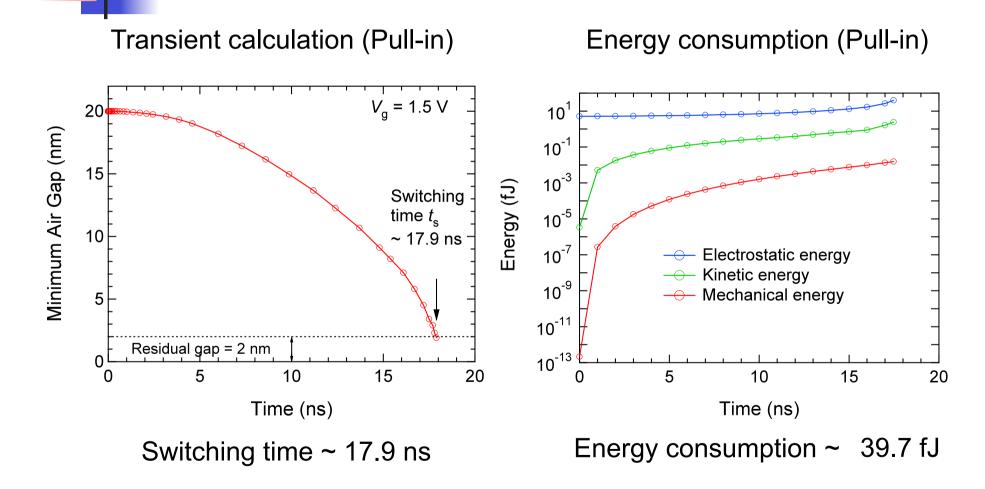

### **Power Management**

### **3D Power Management**

- Area reclaimed on the CMOS Tier

- Signal interconnect length inside/ between gated components,

- "True" VDD (TVDD) supply rings surrounding gated blocks are translated to the NEMS tier.

- Easy to integrate hybrid

- devices technologies

- Low-leakage NEMFET device,

- Energy scavengers,

- Temperature sensors, etc.

- IP Reuse

- Power management controller and always-on cells placed on:

- CMOS tier or NEMS tier.

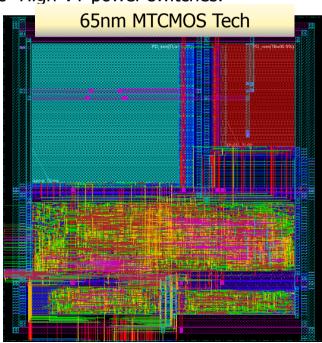

## A Case Study

- Heart beat rate monitor Detects QRS complex in an Digitized Electrocardiogram (ECG).

- Step 1. Identifies the R peaks in the ECG signal.

- Step 2. Measures the interval between two consecutive R peaks.

- Four Designs

- Reference Design 1 TIER design with "classic" High-VT power switches.

- 16-bit openMSP 430

- DMEM 2kB SRAM

- PMEM 4kB ROM

- Peripherals

- Stacked Design 2 TIER design

- Bottom TIER openMSP430 based SoC

- Hybrid Design 2 TIER design

- Bottom TIER openMSP430 based SoC

- Top TIER PSO devices: NEMFETs

- Leakage Enhanced Design 2 TIER design

- Top TIER PSO devices: NEMFETs

- Top TIER PSO and PM Cells: NEMFETs

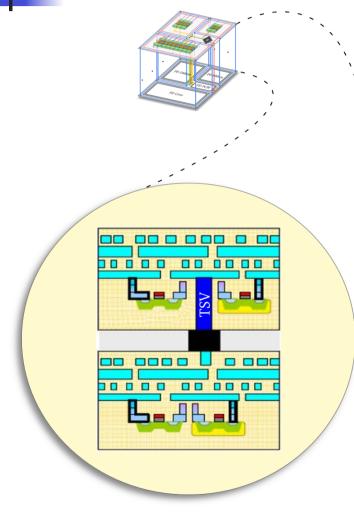

# A Case Study (2)

- Large metal vias connecting adjacent dies

- 5  $\mu$  m diameter

- 20  $\mu$  m length

- 10 μ m pitch

- R ≈ 0.2 Ω / entire TSV → low IR-drop in ON state

- C ≈ 40 fF →

limits the granularity of the power gating

TSV model based on Katti et. al. (IEDM, 2010)

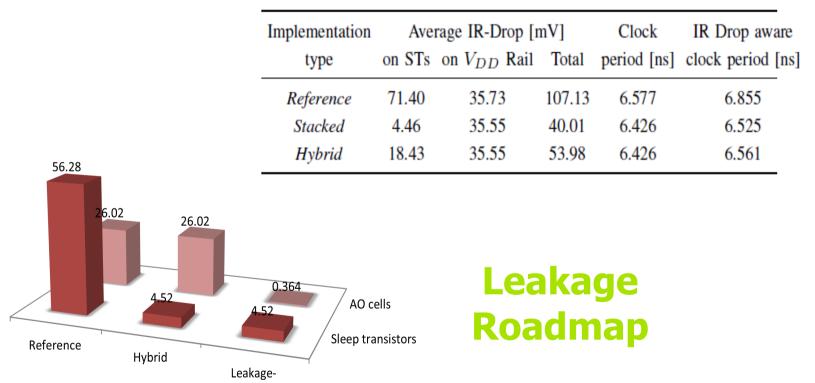

## **Delay and Leakage Analysis**

- Delay degradation

- "interruption" of the power/ground (P/G) rails by the power switch

- IR Drop on the power supply net

enhanced

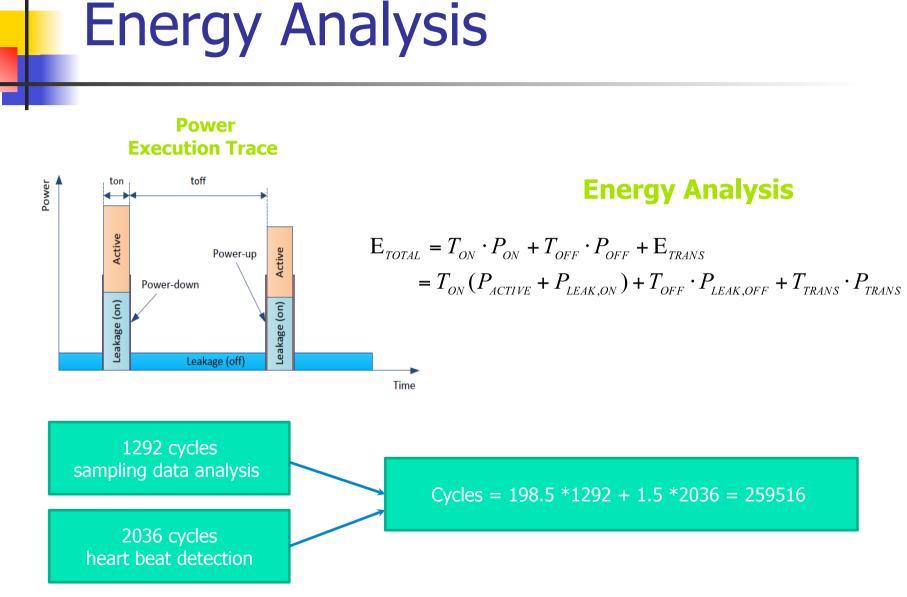

# Energy Analysis (2)

| Implementati<br>on type | ON<br>power<br>[mW] | OFF power [nW] |                     |       | Power-up       | Total          | Energy-<br>Delay   |

|-------------------------|---------------------|----------------|---------------------|-------|----------------|----------------|--------------------|

|                         |                     | STs            | Always-<br>on cells | Total | energy<br>[pJ] | energy<br>[µJ] | Product<br>[µJ·ns] |

| Reference               | 5.0340              | 56.28          | 26.02               | 81.28 | 48.04          | 9.05           | 62.01              |

| Hybrid                  | 5.0339              | 4.52           | 26.02               | 29.52 | 37             | 8.61           | 56.47              |

| Leakage-<br>Enhanced    | 4.7                 | 4.52           | 0.364               | 4.884 | 37             | 8              | 51.48              |

Active time = 1.73 ms, Idle time = 993.35 ms, Transition time = 5.32 ms @ 150 MHz

Improvements

16.64X

17%

- State-of-the-art piezoelectric vibration scavengers from Aktakka et. al.:

- power density of 6.45  $\mu$ W/mm<sup>3</sup>/g<sup>2</sup>

- Our assumptions:1g constant acceleration

=> for 8µJ, 1,24mm<sup>3</sup>

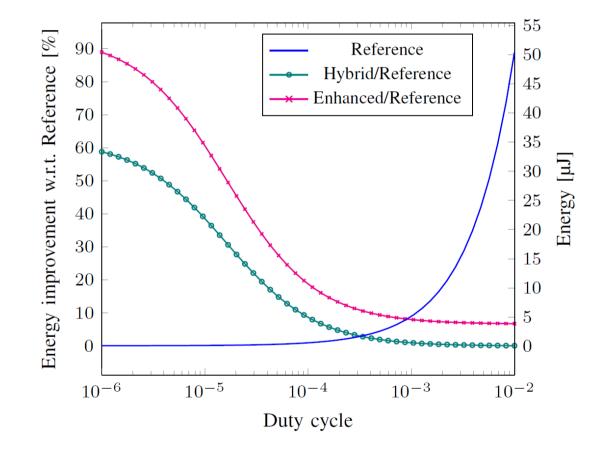

#### Duty Cycle vs. Energy Improvement

- The proposed architecture can help ubiquitous embedded nanosystems cope with very tight energy budgets.

- Promising candidate in reaching truly "zero-energy" ubiquitous nano-systems.

- Specifically effective for low activity applications.

- Energy evaluation of the Enhanced design indicated a reduction of 7% over the 3D Hybrid architecture and of about 15% with respect to the 2D CMOS counterpart.

- For applications with lower activity, the potential energy improvement can reach up to 90%, with respect to the 2D CMOS Reference design.